Published in AJSE, Vol:20, Issue: 2 Received on 11<sup>th</sup> October 2020 Revised on 1<sup>st</sup> March 2021 Accepted on 30<sup>th</sup> April 2021

# Design and Evaluation of a 32-bit Carry Select Adder using 4-bit Hybrid CLA Adder

## Muhammad Saddam Hossain and Farhadur Arifin

Abstract—Adder circuits play a remarkable role in modern microprocessor. Adders are widely used in critical paths of arithmetic operation such as multiplication and subtraction. A Carry Select Adder (CSA) design methodology using a modified 4-bit Carry Look-Ahead (CLA) Adder has been proposed in this research. The proposed 4-bit CLA used hybrid logic style based logic circuits for Carry Generate (Gi) and Carry Propagate (Pi) functions in order to improve performance and reduce the number of transistors required. The modified 4-bit CLA is introduced as the basic unit for implementation of 32-bit CSA. The proposed design of hybrid CLA based 32-bit CSA has been compared with conventional static CMOS based 32-bit CSA and 32-bit Ripple Cary Adder (RCA) by conducting simulation using Cadence Virtuoso tools. Power consumption and delay in the proposed 32-bit CSA are found as 322.6  $\mu$ W and 0.556 ns whereas those parameters in the conventional 32-bit CSA were 455.4  $\mu W$  and 0.667 ns respectively. We have done all the simulation using Cadence Virtuoso 90 nm technology library.

*Index Terms*—carry save adder, carry look-ahead adder, ripple carry adder, hybrid logic.

# I. INTRODUCTION

HE rapid advancement and progress in electronics **L** device has resulted in implementation of several highly intelligent and smart systems which have become essential in making our everyday life easy and comfortable [1-4]. These smart and intelligent systems require high-performance and cost-effective processors for which advanced circuit designs are of outmost necessity [5-7]. Therefore, Performance improvement of VLSI circuit designs plays a crucial role in modern circuits and systems [8].

One of the important subcomponent of VLSI system is digital adders. Designing of Adder has always gained high priority among researchers due to its extensive utilization in Arithmetic Logic Unit (ALU) in modern days [9]. Adders required in subtraction [10], multiplication [11], binary magnitude comparison circuit [12] and in various arithmetic circuits [13-14]. Modern computers processors are mostly implemented on 32 or 64 bits architecture [15-16]. Therefore, requirement of wide adders have become essential. Wide adder in Ripple Carry Adder (RCA) style results in excessive delay due to propagation of signals though the adder stages [17-18]. This excessive delay is not acceptable in modern VLSI circuits for which the concept of Parallel Prefix Adder (PPA) has evolved [19]. CLA [20], CSA [21], Carry Save Adder [22], Carry-Skip Adder [23], Manchester Carry Chain [24] are some of the well-known PPAs.

CLA is considered as the most common adder topology among the PPAs for which extensive research has been conducted on this topic [25]. However, Majority of the research on CLA have been performed on logic and algorithm generation while only a handful amount of work in transistor level design have been conducted [26-30]. Therefore, it is quite necessary to develop a transistor level design of CLA which bring about overall performance of the entire CLA block.

In many design methodologies, 4-bit adder is considered to be a basic block to give rise to wide word length adders [31-32]. Therefore, optimization of 4-bit CLA will bring overall increment in performance of wide word length adder.

We have completed this research in 2 stages working with 3 types of adders. In the first stage, we have designed the conventional 4-bit carry look-ahead adder. Then, we modified the 4-bit CLA adder. We also designed a 4-bit ripple carry adder and made a comparison among conventional 4-bit CLA, modified 4-bit CLA and conventional 4-bit RCA. In the second stage, the proposed 4-bit CLA has been extended to 32-bit in CSA style to test performance in wide word length. The performance of the proposed 32-bit CSA based on 4-bit CLA has been compared with 32-bit conventional CLA based CSA and 32bit RCA. The proposed design showed high-performance compared to the 32-bit RCA and conventional 32-bit CLA based CSA which proves its effectiveness in wide word length adder. We also made another comparison of 32-bit CSA adders which were designed in different ways.

The remaining portion of this article is organized in the following manner. Section II describes the design process of conventional CLA based CSA and RCA. Next, section III presents the proposed 32-bit CSA implementation. After that, simulation results have been presented in section IV. Finally, concluding statement is discussed in section V.

# II. DESIGN OF CONVENTIONAL ADDERS

In this section, the concepts of conventional 4-bit CLA, 32-bit CSA implementation process using 4-bit CLA and 32-bit RCA implementation process is described.

## A. Conventional CLA

A carry look-ahead is a type of adder used in digital logic circuits, that improves speed by reducing the amount of time to determine carry bits. It easily determines one or more carry bits before determining the sum. Thus, it helps to reduce the wait time to determine the higher value bits of an adder.

The conventional 4-bit CLA is implemented using static CMOS logic using carry propagate ( $P_i$ ) and Carry Generate ( $G_i$ ) terms (here 0 < i < 3). If we consider  $A_i$  and  $B_i$  as the input bits which are required to be added, then the  $G_i$  and  $P_i$

Muhammad Saddam Hossain and Farhadur Arifin are with the Department of Electrical and Electronics Engineering, American International University-Bangladesh (AIUB), Dhaka, Bangladesh. (email: saddam.rpc@gmail.com and arifin@aiub.edu)

functions can be written as [33-34]:

$$G_i = A_i B_i \tag{1}$$

$$P_i = A_i \oplus B_i \tag{2}$$

Based on equations (1) and (2), it is clear that  $G_i$  represents AND function between  $A_i$  and  $B_i$  whereas  $P_i$  represents XOR operation between  $A_i$  and  $B_i$ .

The generic equation of 4-bit CLA in conventional style can be stated as [35]:

$$C_{i+1} = G_i + P_i C_i$$

Based on the generic equation, the specific CLA functions can be written as [36-37]:

$$C_{1} = G_{0} + P_{0}C_{0}$$

(3)

$$C_{2} = G_{1} + P_{1}C_{1}$$

(4)

$$= G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 C_0$$

(5)

$$C_4 = G_3 + P_3 C_3$$

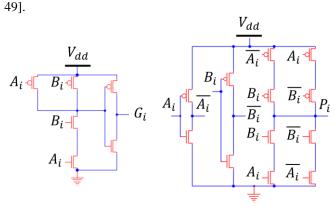

$= G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0 + P_3P_2P_1P_0C_0$  (6) The schematics of the AND and XOR functions in conventional static CMOS logic are shown in Fig. 1. Sum in

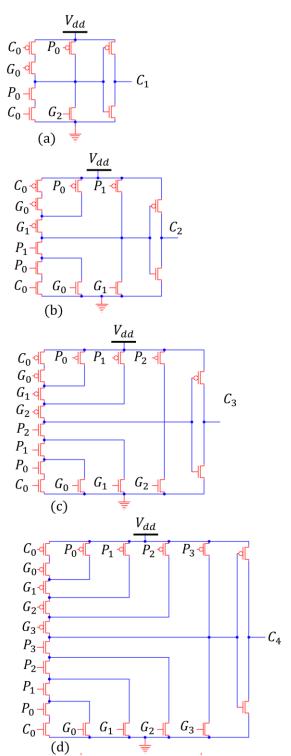

each stage is generated by cascading 2 XOR gates. Based on the above equations, the schematic of the conventional 4-bit CLA carry terms are shown in Fig. 2 [38,

Fig. 1. Transistor level circuits for Conventional AND gate and XOR gate

# B. Conventional CSA using 4-bit CLA

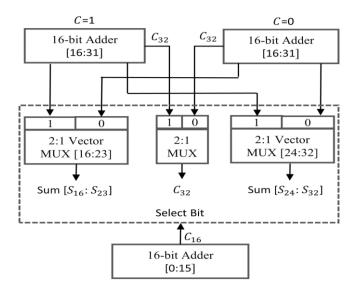

A CSA is a type of logic adder that computes the (n+1)bit sum of 2 n-bit adders. We have designed a 32-bit CSA using 4-bit CLA.

In CSA, the addition process in long chains is broken down into small groups. A n-bit CSA is mainly divided into (n/2)-bit section. In binary carry generation, the carry bit can have two distinct states: logic 0 and logic 1. Therefore,  $C_{n/2}$  bit carry will also have those 2 distinct states:

$$C_{n/2} = 0 \text{ or } C_{n/2} = 1$$

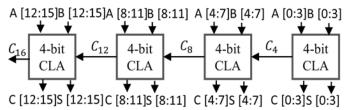

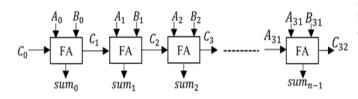

Now, CSA utilizes two adders for upper word and an adder for lower word. Multiplexers are used to enable the necessary upper word based on the signal obtained from the lower word. Block diagram of 32-bit CSA is expressed using Fig. 3 [38]. Here, three individual 16-bit adder, one 2:1 Multiplexer for  $C_{32}$  and 16-bit 2:1 Vector MUX (equivalent to 16 individual 2:1 Mux) are being used [49]. Design process of a 16-bit adder is presented in Fig. 4 where 4-bit CLA is being used as basic block.

Fig. 2. 4-bit CLA Carry Architecture: (a) C1 circuit, (b) C2 Circuit, (c) C3 Circuit, (d) C4 Circuit.

# C. Conventional RCA

A RCA is a logic circuit whereas carry-in of next adder depends on the carry-out of previous adder. Here, sum and carry-out of any adder isn't determined until carry-in of that stage occurs. RCA adder has more delay comparing to other adders because of its long carry chains.

Fig. 3. Design of a 32-bit CSA

Fig. 4. Design of a 16-bit Adder Based on 4-bit CLAs.

Fig. 5. Design of a 32-bit RCA.

Block diagram of a 32-bit RCA process is presented in Fig. 5 [39]. From Fig. 5, it can be understood that RCA possess thirty two full adder (FA) cells. There are various FA based on various logic techniques [40-44]. The adder in [44] would be used here to implement RCA due to its scalability. In RCA, computation of one adder stage needs to wait for its previous adder stage. For this reason, carry signals goes through all the adder stages for which delay increases in wide word length adders.

#### III. DESIGN OF PROPOSED ADDERS

# A. Proposed CLA

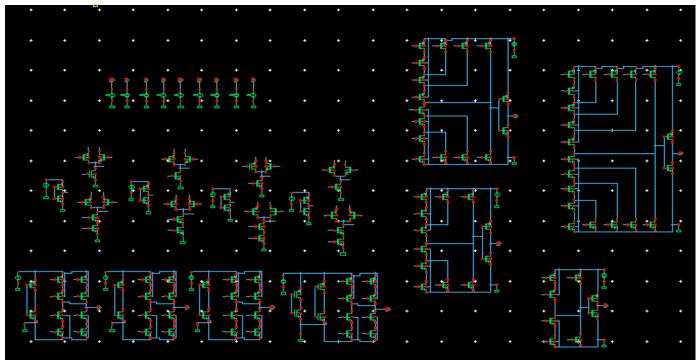

The proposed 4-bit CLA uses the CLA carry terms presented in Fig. 2. However, the changes are made on XOR and AND gates for  $P_i$  and  $G_i$  functions. The proposed XOR and AND gates utilize hybrid logic approach unlike conventional static CMOS process. Truth table for  $G_i$  and  $P_i$  function is presented in Table I.

We have also presented Cadence design of our proposed 4-bit CLA in the Figure 08. The whole design was conducted in Cadence 90nm technology. Here, the connections of the design were completed through virtual wires.

# 1) AND Gate Design

The proposed AND gate for Gi circuit implementation uses hybrid logic style. As per observation of Table 1, the following conditions apply for designing 2-input AND gate:

Condition 1: If  $A_i = B_i = 0$ , then  $G_i = Gnd$  (logic 0)

Condition 2: If  $A_i = 0$ ,  $B_i = 1$ , then  $G_i = A_i$

Condition 3: If  $A_i = 1$ ,  $B_i = 0$ , then  $G_i = B_i = Gnd$

Condition 4: If  $A_i = B_i = 1$ , then  $G_i = A_i$

Based on the conditions 1-4, circuit diagram of the proposed 2-input AND circuit I presented in Fig. 6. As per Fig. 6, the following transistors are responsible for implementing the above-mentioned conditions 1-4.

Condition 1: implemented by  $n_3$

Condition 2: implemented by  $p_2$

Condition 3: implemented by  $n_2$  and  $n_3$

Condition 4: implemented by  $p_2$

2) XOR Gate Design

Unlike 2-input AND circuit, the proposed XOR circuit for Pi implementation uses hybrid logic style as well. As per observation of Table 1, the following conditions apply for designing 2-input XOR gate:

Condition 1: If  $A_i = B_i = 0$ , then  $P_i = A_i = B_i$

Condition 2: If  $A_i = 0$ ,  $B_i = 1$ , then  $P_i = B_i$

Condition 3: If  $A_i = 1$ ,  $B_i = 0$ , then  $P_i = A_i$

Condition 4: If  $A_i = B_i = 1$ , then  $P_i = Gnd$

Based on the above-mentioned conditions 1-4, circuit diagram of the proposed 2-input XOR circuit is presented in Fig. 7. As per Fig. 7, the following transistors are responsible for implementing the above-mentioned conditions 1-4.

Condition 1: implemented by  $p_4$  and  $p_5$ Condition 2: implemented by  $p_5$ Condition 3: implemented by  $p_4$

Condition 4: implemented by  $n_4$  and  $n_5$

Fig. 7. Proposed XOR gate circuit.

Fig. 8. Proposed design of 4-bit CLA

Fig. 9. TG 2:1 MUX used in proposed and conventional CSA.

| TABLE I. | TRUTH TABLE OF $G_I$ and $P_I$ |

|----------|--------------------------------|

|----------|--------------------------------|

| Input |       | Output |       |

|-------|-------|--------|-------|

| $A_i$ | $B_i$ | $G_i$  | $P_i$ |

| 0     | 0     | 0      | 0     |

| 0     | 1     | 0      | 1     |

| 1     | 0     | 0      | 1     |

| 1     | 1     | 1      | 0     |

# B. Proposed 32-bit CSA implemented using Hybrid 4-bit CLA

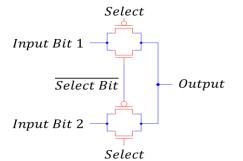

The block diagram for proposed 32-bit CSA is exactly similar to the conventional design in Fig. 3. The main difference lies in the 4-bit CLA part. In addition to the 4-bit CLA, the proposed CSA used Transmission Gate (TG) 2:1 Multiplexers (MUX) rather than using static CMOS logic. The TG 2:1 MUX is presented in Fig. 9.

#### IV. SIMULATION RESULT AND COMPARISON

Performance verification of the proposed and conventional designs is evaluated using Cadence Virtuoso Tool [47]. Standard 90 nm technology node is utilized. Supply and signal voltages are 1 V. We have used channel width and length 120 nm and 100 nm respectively.

Detailed information on the performance of 4-bit adders and 32-bit adders are provided in the following sub-sections.

A. 4-bit adder performance comparison

Performance parameters of 4-bit adder in proposed CLA, conventional CLA and RCA style is stated in Table II. TABLE II. PERFORMANCE OF 4-BIT ADDER

| 4-bit Adder         | Number of<br>Transistors | Power<br>(µW) | Delay (ns) | PDP (fj) |

|---------------------|--------------------------|---------------|------------|----------|

| Conventional<br>CLA | 170                      | 55.4          | 0.16348    | 9.05     |

| RCA                 | 96                       | 16.68         | 0.52159    | 8.70     |

| Proposed CLA        | 130                      | 38.82         | 0.13585    | 5.27     |

From the above table, we can say that the proposed design is considered to be the fastest adder topology while compared with conventional 4-bit CLA and RCA. Power consumption of RCA is lowest due to its less number of transistors [44-46]. The proposed 4-bit CLA also achieved predominant performance in Power Delay Product (PDP).

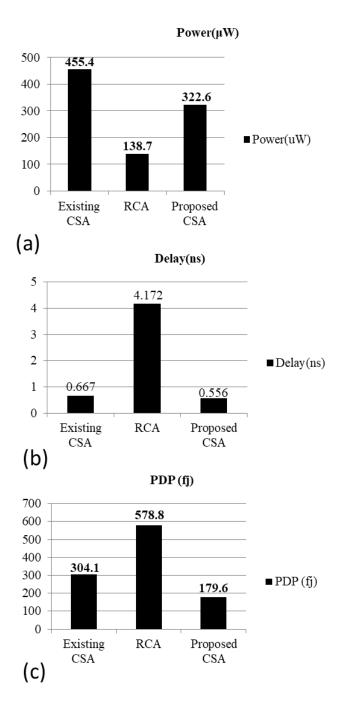

## B. 32-bit adder performance comparison

Performance parameters of 32-bit adder in proposed CSA, conventional CSA and RCA style is stated in Table 3. Graphical representation of the performance aspects has been depicted using Fig. 10. Unlike 4-bit adder, the proposed 32-bit CSA obtained superior speed while RCA obtained superior performance in power. PDP of the proposed 32-bit CSA is the lowest.

| TABLE III. PERFORMANCE OF 32-BIT ADDER | ł |

|----------------------------------------|---|

|----------------------------------------|---|

| 32-bit Adder | Number of   | Power | Delay (ns) | PDP (fj) |

|--------------|-------------|-------|------------|----------|

|              | Transistors | (µW)  |            |          |

|              |             |       |            |          |

| Conventional | 1360        | 455.4 | 0.66792    | 304.1    |

| CSA          |             |       |            |          |

| RCA          | 768         | 138.7 | 4.1727     | 578.8    |

| Proposed     | 1140        | 322.6 | 0.55685    | 179.6    |

| CSÂ          |             |       |            |          |

Fig. 10. 32-bit adder comparison (a)Power, (b)delay and(c) PDP

We have made another comparison of 32-bit CSA adder using different adder cell. We kept the same environment for the comparison. We have simulated on 90 nm technology using cadence tool and the supply voltage were 1V for all the references. This comparison is presented on Table 4. As presented on the table, [49], [51-52] & [56] presented high power consumption and [48], [50] and [54] had moderate value whereas [55] presented the lowest power consumption among all. In terms of delay, [48-50] and [54] showed a higher delay in comparison to other references. Here, [51] had the highest speed. Moving to the PDP, [53] and [55] had lower PDP. Comparing all the results, [55] had the lowest power but its delay was higher whereas [51] had the lowest delay but its power consumption was very high. On the other hand, our proposed design of 32-bit CSA adder had moderate delay as well as power consumption but it had the lowest PDP which is the key factor to evaluate overall performance. As a result, our proposed design again showed a tremendous performance.

TABLE IV. COMPARISON WITH OTHER REPORTED WORK OF 32-BIT CSA ADDERS OPERATING IN 1V SUPPLY VOLTAGE

| Ref. no   | Power (µW) | Delay (ns) | PDP (fj) |

|-----------|------------|------------|----------|

| [48]      | 350.43     | 0.647      | 226.73   |

| [49]      | 428.01     | 0.663      | 283.77   |

| [50]      | 368.47     | 0.681      | 250.93   |

| [51]      | 408.45     | 0.512      | 208.74   |

| [52]      | 394.5      | 0.614      | 238.21   |

| [53]      | 324.28     | 0.579      | 187.06   |

| [54]      | 342.81     | 0.635      | 213.78   |

| [55]      | 310.5      | 0.625      | 192.04   |

| [56]      | 402.25     | 0.593      | 235.94   |

| This work | 322.6      | 0.566      | 179.63   |

# V. CONCLUSION

A hybrid method of 4-bit CLA adder is presented in this paper. The 4-bit CLA is then extended to 32-bits in CSA style. Performance of the proposed 4-bit CLA and 32-bit CSA is compared with the conventional RCA and CLA. Both the proposed 4-bit CLA and 32-bit CSA achieved predominant performance in speed while dissipating acceptable power. The PDP of the proposed designs (4-bit CLA and 32-bit CSA) were also the lowest as per the simulation conducted. We have also collected few data of different 32-bit CSA designs. Finally, we have presented the data and performed a comparison. Our proposed 32-bit CSA adder showed the best performance in terms of Power, delay and Power delay product. Hence, the PPAs in this work can be highly useful in high-performance ALU design in modern systems.

#### REFERENCES

- A. Amouri, F. Arifin, F. Hannig and J. Teich, "FPGA implementation of an invasive computing architecture," 2009 International Conference on Field-Programmable Technology, Sydney, NSW, 2009, pp. 135-142.

- [2] T. Osman, S. S. Psyche, J. M. Shafi Ferdous and H. U. Zaman, "Intelligent traffic management system for cross section of roads using computer vision," 2017 IEEE 7th Annual Computing and Communication Workshop and Conference (CCWC), Las Vegas, NV, 2017, pp. 1-7.

- [3] M. Hasan, M. H. Anik and S. Islam, "Microcontroller Based Smart Home System with Enhanced Appliance Switching Capacity," 2018 Fifth HCT Information Technology Trends (ITT), Dubai, United Arab Emirates, 2018, pp. 364-367.

- [4] F. Arifin, R. Membarth, A. Amouri, F. Hannig and J. Teich, "FSMcontrolled architectures for linear invasion," 2009 17th IFIP International Conference on Very Large Scale Integration (VLSI-SoC), Florianopolis, 2009, pp. 59-64.

- [5] M. Mahdi, M. A. Hossain, S. Hussain, M. Hasan, H. U. Zama, J. K. Saha, "Effect of doping profile variation on nanoscale cylindrical gate carbon nanotube field-effect transistor: a computational study using nonequilibrium Green's function formalism,"Semiconductor Science and Technology, vol. 36, no. 1, 2020.

- [6] J. Warnock et al., "Circuit and Physical Design of the zEnterprise™ EC12 Microprocessor Chips and Multi-Chip Module," in IEEE Journal of Solid-State Circuits, vol. 49, no. 1, pp. 9-18, Jan. 2014.

- [7] M. Hasan, M. H. Anik, S. Chowdhury, S. A. Chowdhury, T. I. Bilash, S. Islam, Low-Cost Appliance Switching Circuit for Microcontroller-Controlled Smart Home, International Journal of Sensors and Sensor Networks, vol. 2, no. 7, pp. 16-22, 2019.

- [8] M. Li et al., "Energy Optimized Subthreshold VLSI Logic Family With Unbalanced Pull-Up/Down Network and Inverse Narrow-Width Techniques," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 12, pp. 3119-3123.

- [9] S. Roy, M. Choudhury, R. Puri and D. Z. Pan, "Polynomial Time Algorithm for Area and Power Efficient Adder Synthesis in High-Performance Designs," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 35, no. 5, pp. 820-831, May 2016.

- [10] U. B. Joy, S. Chakraborty, S. Tasnim, M. S. Hossain, A. H. Siddique, M. Hasan, "Design of an Area Efficient Quantum Dot Cellular Automata Based Full Adder Cell Having Low Latency," 2021 2nd International Conference on Robotics, Electrical and Signal Processing Techniques (ICREST), Dhaka, Bangladesh, 2021, pp. 689-693.

- [11] E. Antelo, P. Montuschi and A. Nannarelli, "Improved 64-bit Radix-16 Booth Multiplier Based on Partial Product Array Height Reduction," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 2, pp. 409-418, Feb. 2017.

- [12] M. Hasan, U. K. Saha, M. S. Hossain, P. Biswas, M. J. Hossein and M. A. Z. Dipto, "Low Power Design of a Two Bit Mangitude Comparator for High Speed Operation," 2019 International Conference on Computer Communication and Informatics (ICCCI), Coimbatore, Tamil Nadu, India, 2019, pp. 1-4.

- [13] S. K.C., S. M., G. B.C., L. D.M., Navya and P. N.V., "Performance Analysis of Parallel Prefix Adder for Datapath VIsi Design," 2018 Second International Conference on Inventive Communication and Computational Technologies (ICICCT), Coimbatore, 2018, pp. 1552-1555.

- [14] M. Hasan, M. J. Hossein, U. K. Saha and M. S. Tarif, "Overview and Comparative Performance Analysis of Various Full Adder Cells in 90 nm Technology," 2018 4th International Conference on Computing Communication and Automation (ICCCA), Greater Noida, India, 2018, pp. 1-6.

- [15] K. A. K. Maurya, Y. R. Lakshmanna, K. B. Sindhuri and N. U. Kumar, "Design and implementation of 32-bit adders using various full adders," 2017 Innovations in Power and Advanced Computing Technologies (i-PACT), Vellore, 2017, pp. 1-6.

- [16] Wei Hwang, G. Gristede, P. Sanda, S. Y. Wang and D. F. Heidel, "Implementation of a self-resetting CMOS 64-bit parallel adder with enhanced testability," in IEEE Journal of Solid-State Circuits, vol. 34, no. 8, pp. 1108-1117.

- [17] K. Papachatzopoulos and V. Paliouras, "Static Delay Variation Models for Ripple-Carry and Borrow-Save Adders," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 7, pp. 2546-2559, July 2019.

- [18] V. Pudi and K. Sridharan, "Low Complexity Design of Ripple Carry and Brent–Kung Adders in QCA," in IEEE Transactions on Nanotechnology, vol. 11, no. 1, pp. 105-119, Jan. 2012.

- [19] S. Khan and Z. A. Jaffery, "Parallel-prefix modulo adders: A Review," 2017 14th IEEE India Council International Conference (INDICON), Roorkee, 2017, pp. 1-5.

- [20] M. Hasan, A. H. Siddique, A. H. Mondol, M. Hossain, H. U. Zaman, S. Islam, "High-performance design of a 4-bit Carry Look-Ahead Adder in static CMOS logic," Indonesian Journal of Electrical Engineering and Informatics, vol. 8, no. 4, pp. 666-673, 2020.

- [21] M. Hasan, M. S. Hossain, A. H. Siddique, M. Hossain, H. U. Zaman, S. Islam, "A high-speed 4-bit carry look-ahead architecture as a building block for wide word-length Carry-Select Adder," Microelectronics Journal, vol. 109, 2021.

- [22] R. Mahalakshmi and T. Sasilatha, "A power efficient carry save adder and modified carry save adder using CMOS technology," 2013 IEEE International Conference on Computational Intelligence and Computing Research, Enathi, 2013, pp. 1-5.

- [23] S. Patel, B. Garg, A. Mahajan and S. Rai, "Area-Delay Efficient and Low-Power Carry Skip Adder for High Performance Computing Systems," 2019 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), Rourkela, India, 2019, pp. 300-303.

- [24] J. Asha and J. Senthilkumar, "High speed Manchester Carry chain with carry-skip capability," 2015 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2015], Nagercoil, 2015, pp. 1-7.

- [25] M. Hasan, M. S. Islam, M. R. Ahmed, "Performance Improvement of 4-Bit Static CMOS Carry Look-Ahead Adder Using Modified Circuits for Carry Propagate and Generate Terms," Science Journal of Circuits, Systems and Signal Processing, vol. 8, no. 2, pp. 76-81, 2019.

- [26] C. Efstathiou, Z. Owda and Y. Tsiatouhas, "New High-Speed Multioutput Carry Look-Ahead Adders," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 60, no. 10, pp. 667-671, Oct. 2013.

- [27] O. Akbari, M. Kamal, A. Afzali-Kusha and M. Pedram, "RAP-CLA: A Reconfigurable Approximate Carry Look-Ahead Adder," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 8, pp. 1089-1093, Aug. 2018.

- [28] S. Ghafari, M. Mousazadeh, A. Khoei and A. Dadashi, "A New Highspeed and Low area Efficient Pipelined 128-bit Adder Based on Modified Carry Look-ahead Merging with Han-Carlson Tree Method," 2019 MIXDES - 26th International Conference "Mixed Design of Integrated Circuits and Systems", Rzeszów, Poland, 2019, pp. 157-162.

- [29] N. J. Lisa and H. M. H. Babu, "Design of a Compact Reversible Carry Look-Ahead Adder Using Dynamic Programming," 2015 28th International Conference on VLSI Design, Bangalore, 2015, pp. 238-243.

- [30] S. Lubaba, K. M. Faisal, M. S. Islam and M. Hasan, "Design of a Two-Bit Magnitude Comparator Based on Pass Transistor, Transmission Gate and Conventional Static CMOS Logic," 2020 11th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kharagpur, India, 2020, pp. 1-5.

- [31] W. Cheng, J. Hu, "A structured approach for optimizing 4-bit carry look-ahead adder," The Open Electrical and Electronic Engineering Journal, vol. 8, pp. 133-142, 2014.

- [32] S. J. Gladwin, M. Mangayarkkarasi, Design and performance comparison of 4-bit adders using different logic styles, Journal of Computational and Theoretical Nanoscience, vol 15, no. 3, pp. 949-960, 2018.

- [33] M. Valinataj, Fault-tolerant carry look-ahead adder architectures robust to multiple simultaneous errors, Microelectronics Reliability, vol. 55, no. 12, pp. 2845-2857, 2015.

- [34] N. H. E. Weste, D. Harris, and A. Banerjee, CMOS VLSI Design: A Circuits and Systems Perspective, 3rd ed. Delhi, India: Pearson Education, 2010.

- [35] R. H. V and S. Hiremath, "Low Power Design and Implementation of Multi-Output Carry Look-Ahead Adder," 2018 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 2018, pp. 1912-1916.

- [36] M. Hasan, P. Biswas, M. S. Alam, H. U. Zaman, M. Hossain and S. Islam, "High Speed and Ultra Low Power Design of Carry-Out Bit of 4-Bit Carry Look-Ahead Adder," 2019 10th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kanpur, India, 2019, pp. 1-5.

- [37] M. Binggeli, S. Denton, N. S. Muppaneni and S. Chiu, "Optimizing carry-lookahead logic through a comparison of PMOS and NMOS block inversions," 2015 IEEE International Conference on Electro/Information Technology (EIT), Dekalb, IL, 2015, pp. 641-646.

- [38] G. A. Ruiz, M. Granda, "An area-efficient CMOS carry-select adder based on a compact carry look-ahead unit," Microelectronics Journal, vol. 35, no. 12, pp. 939-944, 2004.

- [39] M. Sarkar, G. S. Taki, Prerna, R. Sengupta and S. N. Ray, "Design of ripple carry adder using CMOS output wired logic based majority gate," 2017 8th Annual Industrial Automation and Electromechanical Engineering Conference (IEMECON), Bangkok, 2017, pp. 328-331.

- [40] M. Hasan, M. J. Hossein, M. Hossain, H. U. Zaman and S. Islam, "Design of a Scalable Low-Power 1-Bit Hybrid Full Adder for Fast Computation," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 8, pp. 1464-1468, 2020.

- [41] H. Naseri and S. Timarchi, "Low-Power and Fast Full Adder by Exploring New XOR and XNOR Gates," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 8, pp. 1481-1493, Aug. 2018.

- [42] M. Hasan, H. U. Zama, M. Hossain, P. Biswas, S. Islam, "Gate Diffusion Input technique based full swing and scalable 1-bit hybrid full adder for high performance applications," Engineering Science and Technology, An International Journal, vol. 23, no. 6, pp. 1364-1373, 2020.

- [43] V. Foroutan, M. R. Taheri, K. Navi, A. A. Mazreah, "Design of two low-power full adder cells using GDI structure and hybrid CMOS logic style," Integration, vol. 47, no. 1, pp. 48-61, 2014.

- [44] M. Hasan, U. K. Saha, A. Sorwar, M. A. Z. Dipto, M. S. Hossain and H. U. Zaman, "A Novel Hybrid Full Adder Based on Gate Diffusion Input Technique, Transmission Gate and Static CMOS Logic," 2019 10th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kanpur, India, 2019, pp. 1-6.

- [45] B. R. Zeydel, D. Baran and V. G. Oklobdzija, "Energy-Efficient Design Methodologies: High-Performance VLSI Adders," in IEEE Journal of Solid-State Circuits, vol. 45, no. 6, pp. 1220-1233, June 2010.

- [46] S. Chandra, K. Lahiri, A. Raghunathan and S. Dey, "Variation-Tolerant Dynamic Power Management at the System-Level," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 17, no. 9, pp. 1220-1232, Sept. 2009.

- [47] Cadence, available at "https://www.cadence.com/en\_US/home.html"

- [48] G.K. Reddy and S. B. Rao, "A comparative study on low-power and high speed Carry Select Adder," 2015 IEEE 9th International Conference on Intelligent Systems and Control (ISCO), Coimbatore, India.

- [49] A.P. Thakare, S. Agrawal and V. Tiwari, "32 Bit Carry Select Adder with BEC-1 Technique," Sixth IRAJ International Conference, 6th October 2013, Pune, India.

- [50] Rashmi S.B and V. Oli, "32 bit power efficient carry select adder using 4T XNOR gate," 2016 2nd International Conference on Applied and Theoretical Computing and Communication Technology (iCATccT), Bangalore, 2016, pp. 283-287.

- [51] Archit Bajpai, A.R. Anurag, G. Shakthivel, B.S Premananda, "Design of Low Power and High-Speed 16-bit Square Root Carry Select Adder using AL," 2018 3rd International Conference on Circuits, Control, Communication and Computing, Bangalore, India

- [52] A.R Hebbar, P. Srivastava, V.K Joshi, "Design of High Speed Carry Select Adder using Modified Parallel Prefix Adder," 8th International Conference on Advances in Computing and Communication (ICACC-2018)

- [53] A. Naik, D. Deka, D. Pal, "ASIC Implementation of High-Speed Adaptive Recursive Karatsuba Multiplier with Square-Root-Carry-Select-Adder," 2020 IEEE 11th Latin American Symposium on Circuits & Systems (LASCAS), San Jose, Costa Rica

- [54] B.S. Kandula, P.V Kalluru, S.P Inty, "Design of area efficient VLSI architecture for carry select adder using logic optimization technique," Willey online library, 27 May 2020

- [55] V. Dhandapani (2017), "An Efficient Architecture for Carry Select Adder," World Journal of Engineering, Vol. 14, Issue: 3,pp

- [56] B. S. Premananda, M. K. Chandana, K. P. Shree Lakshmi, A. M. Keerthi, "Design of Low Power 8-Bit Carry Select Adder Using Adiabatic Logic," 2017 International Conference on Communication and Signal Processing (ICCSP), Chennai, India

Muhammad Saddam Hossain received his Bachelor degree in Electrical and Electronic Engineering from North South University, Dhaka, Bangladesh in 2017. After that, he completed M.Sc in Electrical and Electronic Engineering from American International University,

Dhaka, Bangladesh in the year of 2020. Currently, he is working as a Service Engineer at Fresenius Medical Care Bangladesh Limited. Previously he worked as an Assistant Engineer in Globex Marketing Company Limited from 2017 to 2020. He has a published paper in IEEE as a first author. He also acted as a co-author in several IEEE sponsored papers and a journal. His Research interest lies in VLSI, Electronics, Biomedical Appliances and Communication System.

**Farhadur Arifin** received his B.Sc. Degree in Electrical and Electronic Engineering from Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh in 2000, and M.Sc. Degree in Electrical Engineering from Royal Institute of Technology (KTH), Stockholm, Sweden in

2005. Currently he is working as an Associate Professor in the department of EEE and CoE at American International University- Bangladesh (AIUB). He is an active IEEE member & volunteer for last 6 years. He has 16 years of teaching and research experiences in different countries and published more than thirty peer-reviewed papers in the domain of electrical and electronic engineering. His research interests include ultra-wide-band (UWB) technology in wireless communications, UWB antennas, VLSI circuit design, System on chip design, RF integrated circuit and biomedical applications.